在晶体管尺寸接近极限时,3D堆叠CMOS技术为摩尔定律的延续开辟了新天地。

过去50年,晶体管不断缩小、集成度提升,功耗降低,成为技术进步的标志。然而,自我们在英特尔开始职业生涯以来,关于微型化的终结警报不绝于耳。尽管如此,半导体行业依然不断创新,推动技术向前发展。

随着晶体管架构的变化,我们逐渐从平面设计转向3D鳍式晶体管。如今,这一技术也面临极限,新的门控全围绕结构即将投入生产。未来,我们的关注将转向第三维度。我们已经创造了高度堆叠的实验设备,能够将逻辑电路的体积缩小30%至50%。这种3D堆叠的互补金属氧化物半导体(CMOS)——互补场效应晶体管(CFET),有望延续摩尔定律。

晶体管的演变

摩尔定律的持续创新伴随权衡,每一项进展都带来新的挑战。了解晶体管的基本结构有助于我们理解这些权衡。每个金属氧化物半导体场效应晶体管(MOSFET)由门堆叠、通道、源和漏组成。源和漏的掺杂类型决定了它们的电导特性,而通道区域则与之相反。

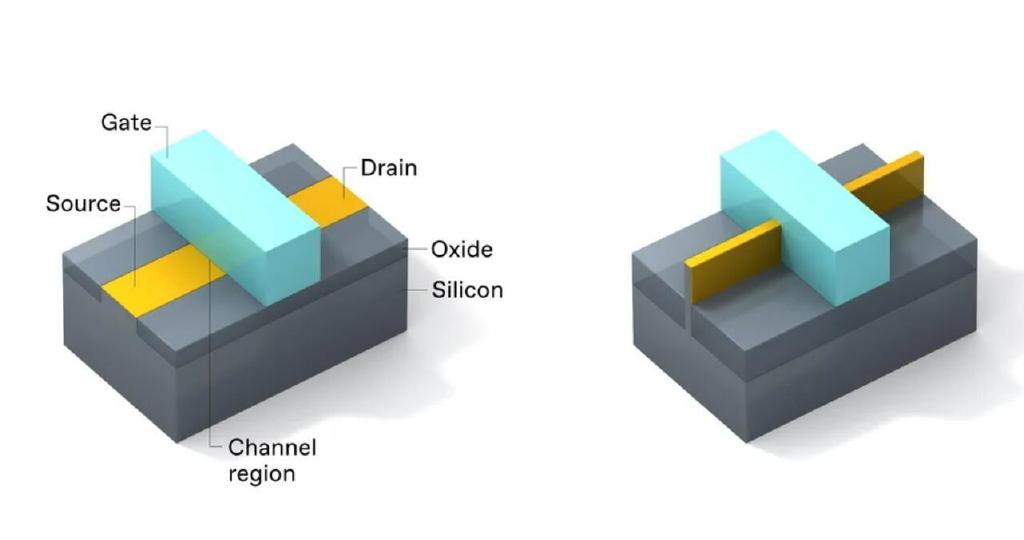

从平面晶体管架构[左]到FinFET [右]的转变提供了对沟道的更大控制[由蓝框覆盖],从而降低了50%的功耗,并提高了37%的性能。

在2011年之前,平面MOSFET的门堆叠位于通道之上,施加电压形成移动电荷层,实现电流流动。然而,随着晶体管的缩小,出现了短通道效应,导致电流泄漏。为此,行业转向了鳍式晶体管(FinFET),这种设计在三面包裹通道,提供了更好的电场控制。

英特尔在2011年推出了FinFET,标志着摩尔定律的又一次飞跃。FinFET在更低电压下运行,减少了功耗,并提高了性能。然而,FinFET的宽度离散化限制了设计灵活性,迫切需要新的解决方案。

新一代RibbonFET,作为自FinFET以来的首个新架构,门完全包围通道,采用纳米级硅带状结构,彻底解决了宽度量化问题。通过堆叠的设计,设备在不增加面积的情况下提升了电流驱动能力。

堆叠CMOS的优势

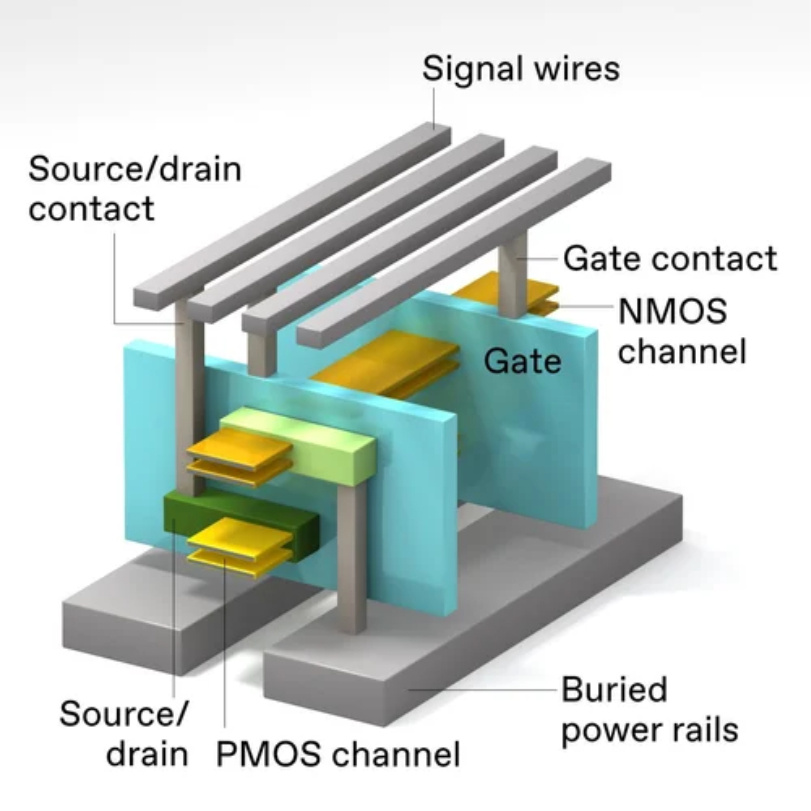

平面、FinFET和RibbonFET晶体管都基于CMOS技术,NMOS和PMOS的结合使其在1980年代成为主流。通过将NMOS放置于PMOS之上,我们在2019年首次提出3D堆叠晶体管的概念,并在2020年展示了首个基于此技术的逻辑电路设计。

3D堆叠CMOS面临诸多制造挑战,但我们采用了自对准工艺,能够在一个步骤中构建NMOS和PMOS。通过这种方法,我们能有效减少制造步骤,降低成本,同时避免了晶圆对接时的对准问题。

将所有需要的连接连接到3D堆叠CMOS是一项挑战。电源连接需要从设备堆栈下方进行。在该设计中,NMOS器件[顶部]和PMOS器件[底部]具有单独的源极/漏极接触,但两个器件具有公共的栅极。

摩尔定律的未来

有了RibbonFET和3D CMOS,我们为摩尔定律的延续找到了一条清晰的道路。正如戈登·摩尔所言,技术进步常常超出想象。我们相信,随着新技术的不断发展,摩尔定律将在未来继续焕发活力。

本文译自 IEEE Spectrum,由 BALI 编辑发布。